NPTEL Advanced Computer Architecture Week 7 Assignment Answers 2025

1. Which of the following statements is true?

- A streaming multiprocessor (SM) has generic processing blocks.

- A streaming multiprocessor (SM) does not have memory structures.

- A TPC (Texture Processing Cluster) doesn’t contain a polymorph engine.

- A streaming multiprocessor (SM) has multiple TPCs (Texture Processing Clusters).

Answer :- For Answers Click Here

2. The ___________ in a ___________ is specialized for matrix multiplication. Each PB has an __________ instruction cache.

- tensor core, processing block (PB), L1

- processing block (PB), tensor core, L1

- tensor core, processing block (PB), L0

- processing block (PB), tensor core, L0

Answer :-

3. Consider the following statements and select the appropriate answer.

S1: A warp has a single program counter.

S2: Multiple threads within a warp can run in parallel.

- Only S1 is true

- Only S2 is true

- Both S1 and S2 are true

- Both S1 and S2 are false

Answer :-

4. Which statement is TRUE about cache size?

- A bigger cache is always better for performance.

- Smaller caches are always better for performance.

- The cache size shouldn’t matter as long as the main memory is large.

- The ideal size depends on the application and memory access patterns.

Answer :-

5. Cache memory is faster than main memory because

- It uses SRAM technology.

- It uses DRAM technology.

- It employs advanced data compression techniques.

- It is periodically refreshed.

Answer :-

6. In a direct-mapped cache, the data and tag array are accessed ____________ for read requests. Destructive interference leads to cache ____________.

- in parallel, hits

- in parallel, misses

- serially, hits

- serially, misses

Answer :- For Answers Click Here

7. Which cache mapping technique allows a block to be placed in any line of the cache?

- Direct-mapped

- Skew-Associative

- Set-associative

- Fully associative

Answer :-

8. A computer system utilizes a 8-way set-associative cache with a capacity of 64 KB, a block size of 16 bytes, and a 32-bit address space. Determine the number of bits needed for the tag field in this cache organization.

- 19

- 32

- 28

- 11

Answer :-

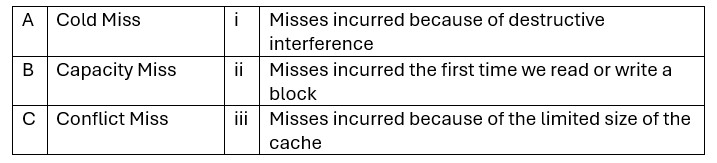

9. Match the following and select the appropriate option.

A-i, B-ii, C-iii

A-ii, B-i, C-iii

A-iii, B-ii, C-I

A-ii, B-iii, C-i

Answer :-

10. Consider the following statements and select the most appropriate option.

S1: To reduce address translation overheads, we use a small cache of mappings between pages and frames known as the Translation Lookaside Buffer (TLB).

S2: It is necessary to access the TLB every time we issue a load/store request to the memory system.

- Only S1 is true

- Only S2 is true

- Both S1 and S2 are true

- Both S1 and S2 are false

Answer :- For Answers Click Here