NPTEL Digital System Design Assignment Answers 2025

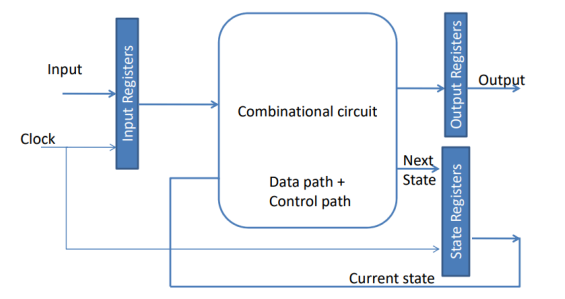

1. For the given figure, which of the following statements is correct?

- The combinational circuit computes the current state from the output registers

- The clock signal is not required for state transitions in the system.

- The state registers store the current state and provide it as an input to the combinational circuit.

- The output registers store the next state of the system directly.

Answer :- For Answers Click Here

2. Which of the following statements about RTL modeling in Verilog is correct?

- The assign statement is used for describing sequential logic.

- The always block with the @posedge clock trigger is used to model sequential logic.

- Combinational logic cannot be described using the assign statement.

- Non-blocking statements (<=) are not permissible in RTL modeling.

Answer :-

3. Which of the two operators represents a non-blocking assignment in Verilog?

- “=”

- “<=”

Answer :-

4. When finding the worst-case critical path and deciding the clock period, which of the following statements is true?

- One operation can dominate the circuit’s delay.

- The overall execution time depends on the slowest operation.

- Both a and b.

- None of the above.

Answer :-

5. When deciding the clock period, which of the following is NOT a valid design principle?

- Impose specific timing or performance constraints on the design to meet clock period requirements.

- Slow operations are converted into multi-cycle operations.

- Clock period is decided by the fastest operation.

- Critical path must be carefully considered in the design.

Answer :- For Answers Click Here

6. A typical RTL (Register Transfer Level) design implementation involves state machines that control which operation is executed during each clock cycle.

- True

- False

Answer :-

7. What operation does the given pseudo-code implement?

- Finding the sum of two numbers.

- Calculating the greatest common divisor (GCD) of two numbers.

- Computing the difference between two numbers.

- Checking if two numbers are equal.

Answer :-

8. What happens when x is initially equal to y in the given code?

- The loop executes until x becomes 0.

- The loop is skipped, and z is set to x.

- An infinite loop occurs.

- x and y are continuously decremented by 1.

Answer :-

9. What is the significance of the eoc = 1 statement in the code?

- It resets the inputs xx and yy.

- It signals that the computation is complete.

- It starts the next iteration of the loop.

- It terminates the program execution.

Answer :- For Answers Click Here